# Metrology challenges for the semiconductor industry

#### **An ASML Perspective**

Wim Coene and Lorenzo Tripodi ASML-Research, Metrology Department

July 8<sup>th</sup> 2022 Veldhoven, The Netherlands

wim.coene@asml.com lorenzo.tripodi@asml.com

EURAMET – Meeting "Open Consultation on Semiconductor Metrology" July 8<sup>th</sup> 2022

- Introducing ASML

- Holistic Patterning Triangle and Overlay Metrology

- From Overlay metrology to EPE<sup>(\*)</sup> metrology

- Landscape of Technologies for Semicon Metrology

#### Introducing ASML

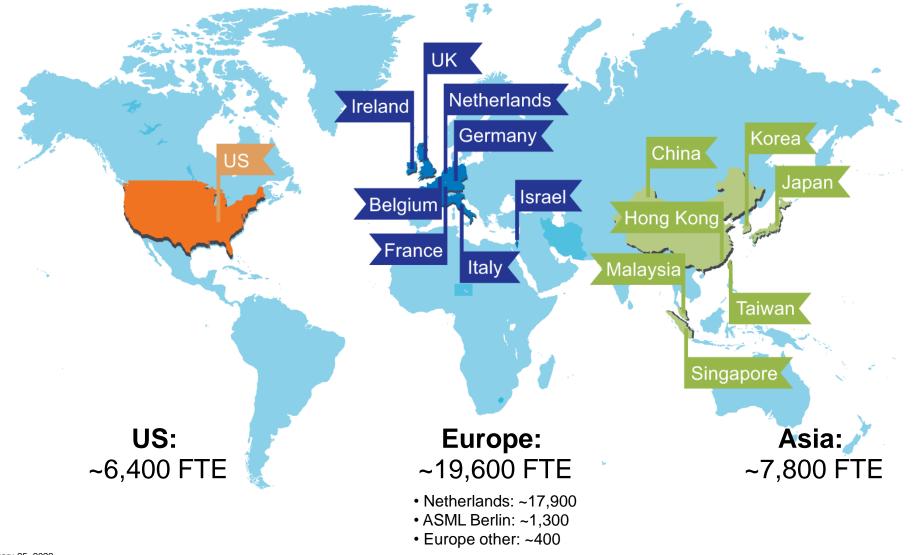

#### A global presence with ~34,000 employees (Q1 2022)

Offices in over 60 cities in 16 locations worldwide

- Introducing ASML

- Holistic Patterning Triangle and Overlay Metrology

- From Overlay metrology to EPE<sup>(\*)</sup> metrology

- Landscape of Technologies for Semicon Metrology

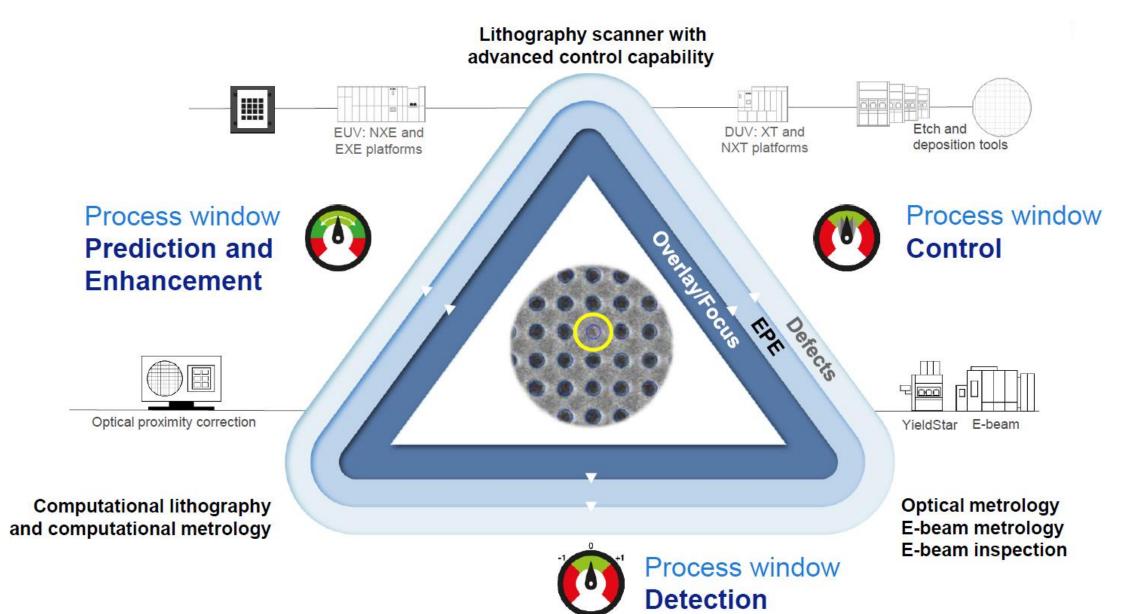

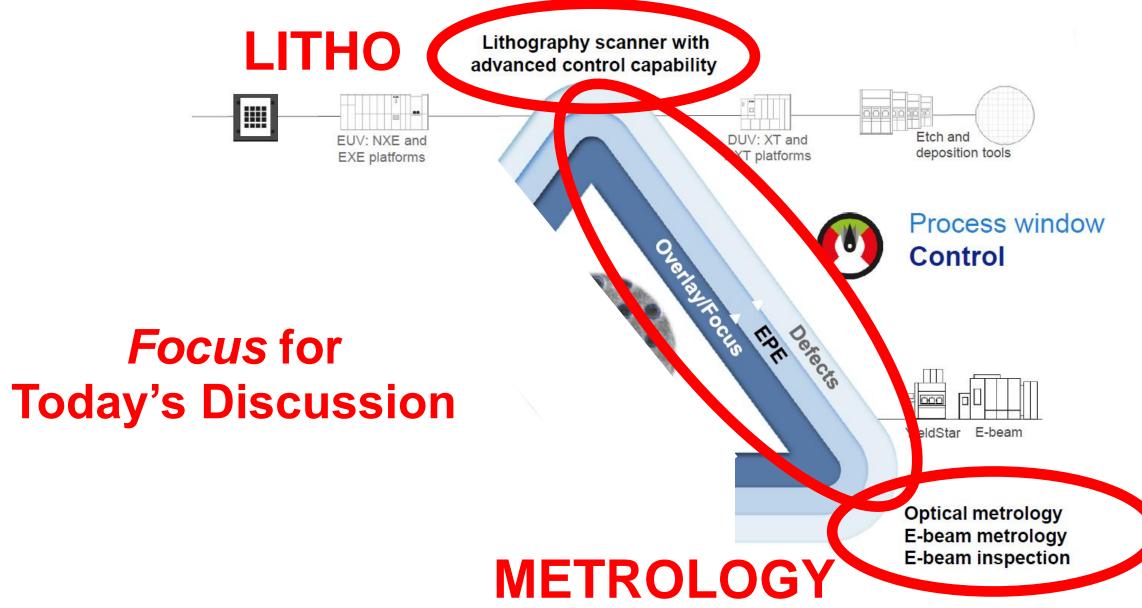

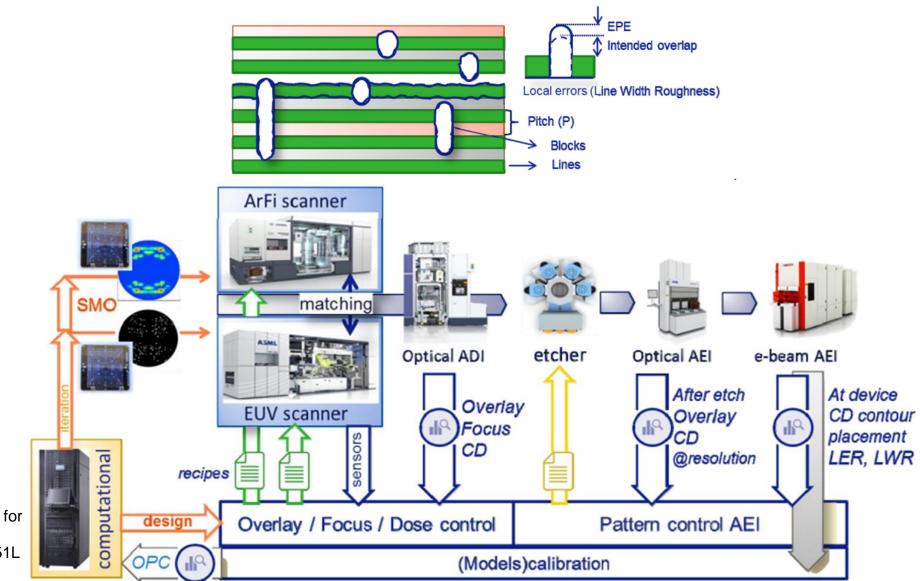

### Metrology @ ASML : one of the 3 key-elements of Holistic Patterning

### Metrology @ ASML : one of the 3 key-elements of Holistic Patterning

#### Metrology @ ASML : one of the 3 key-elements of Holistic Patterning ASML

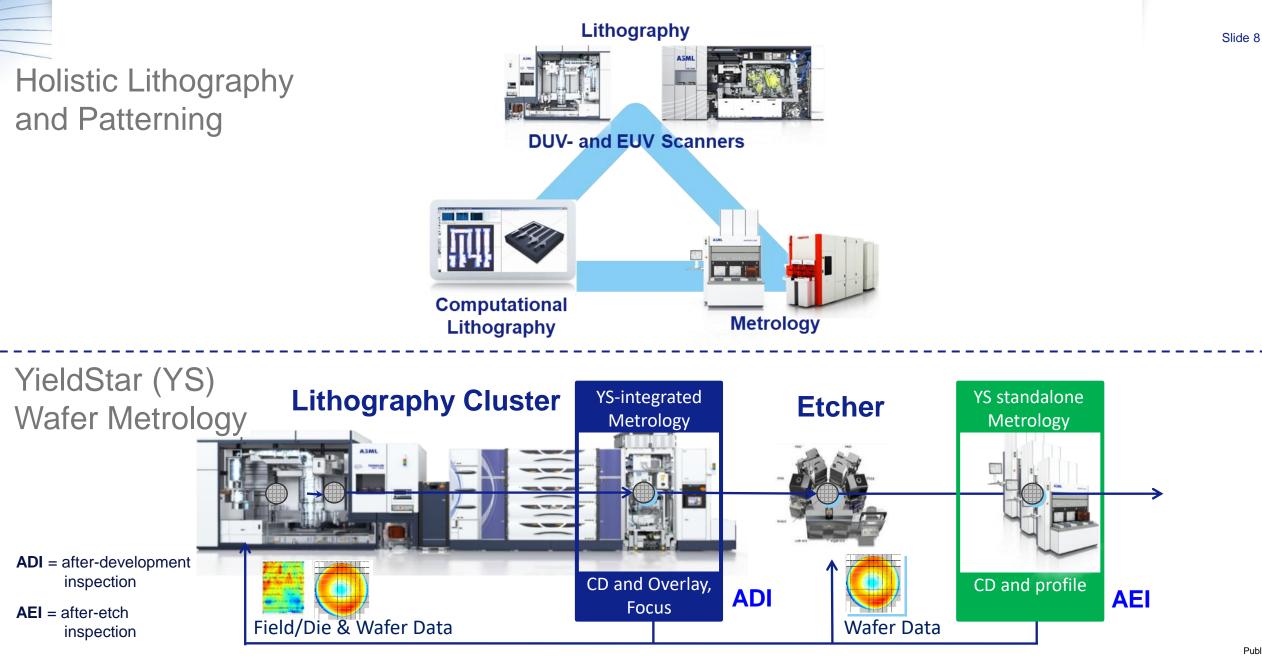

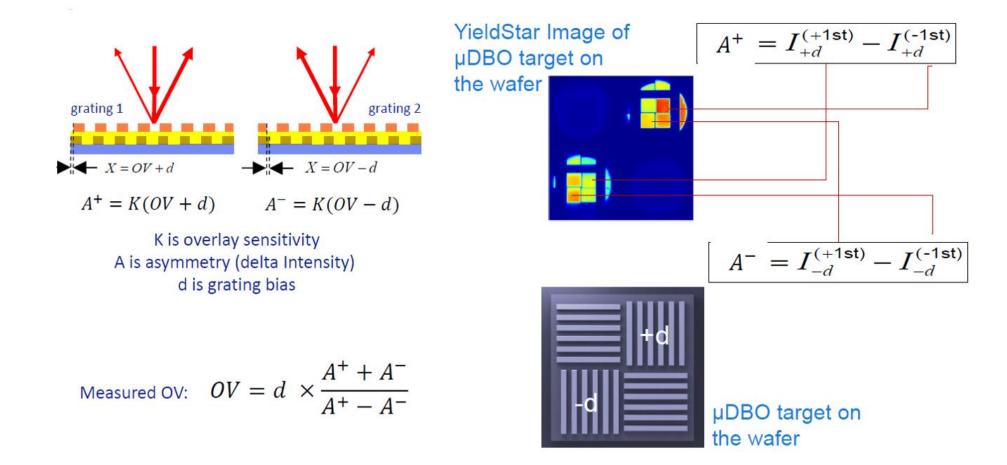

#### *Current* Optical METROLOGY @ ASML : mainly diffraction-based overlay metrology (DBO for ADI)

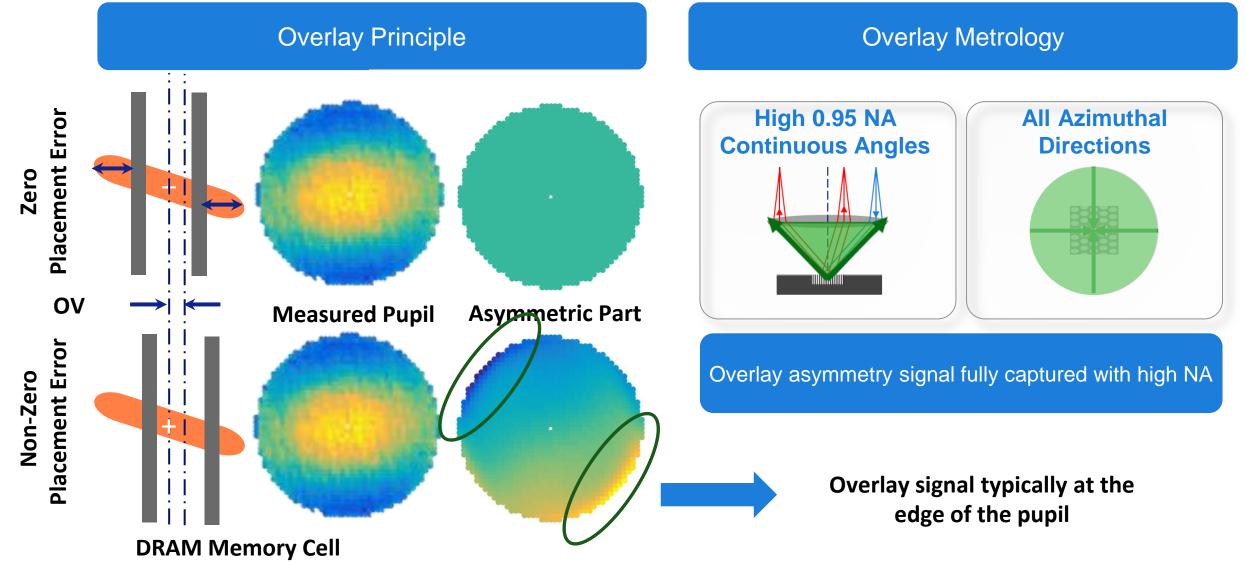

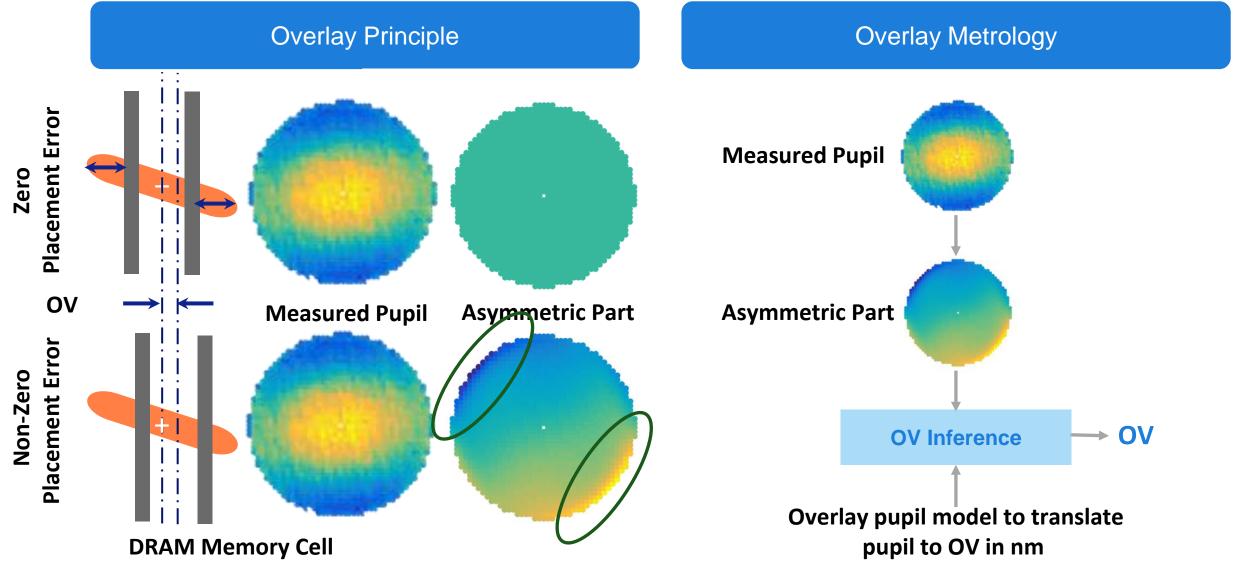

# In-Device Metrology (IDM) Overlay: Concept

**Oth-Order Pupil Asymmetry signals are a measure for Overlay**

# In-Device Metrology (IDM) Overlay: Concept

**Oth-Order Pupil Asymmetry signals are a measure for Overlay**

May 12, 2022

- Introducing ASML

- Holistic Patterning Triangle and Overlay Metrology

- From Overlay metrology to EPE<sup>(\*)</sup> metrology

- Landscape of Technologies for Semicon Metrology

# From overlay-metrology towards EPE<sup>(\*)</sup>-metrology

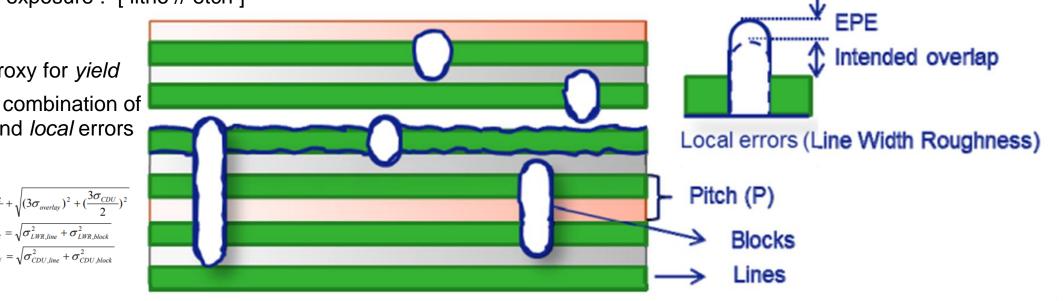

#### Multiple patterning DUV + EUV

- **1D-grating** with DUV (193nm) + Self-Aligned-Quadruple-Patterning (SAQP)

- Multiple exposures : [ litho // etch ]<sup>n</sup>

- Cut-pattern of 2D block-structure with EUV (13.5nm)

- Single exposure : [ litho // etch ]

• EPE is the better proxy for *yield*

EPE results from a combination of global (CD, OVL) and local errors (LWR, LER)

$EPE_{\max} = \frac{HalfRange_{OPC}}{2} + \frac{3\sigma_{PBA}}{2} + \frac{6\sigma_{LWR}}{\sqrt{2}} + \sqrt{(3\sigma_{overlay})^2 + (\frac{3\sigma_{CDU}}{2})^2}$ with  $\sigma_{LWR} = \sqrt{\sigma_{LWR,line}^2 + \sigma_{LWR,block}^2}$ and  $\sigma_{CDU} = \sqrt{\sigma_{CDU,line}^2 + \sigma_{CDU,block}^2}$

EPE<sup>(\*)</sup> = edge placement error

Jan Mulkens et al, Metrology, Inspection, and Process Control for Microlithography XXXII, Proc. of SPIE Vol. 10585, 105851L ASML May 12, 2022

### From overlay-metrology towards EPE-metrology (2)

Jan Mulkens et al, Metrology, Inspection, and Process Control for Microlithography XXXII, Proc. of SPIE Vol. 10585, 105851L

- Introducing ASML

- Holistic Patterning Triangle and Overlay Metrology

- From Overlay metrology to EPE<sup>(\*)</sup> metrology

- Landscape of Technologies for Semicon Metrology

### Semi-Con METROLOGY: Landscape of Diverse Needs & Technologies

#### **NEEDS**

- Overlay Metrology

- EPE-Metrology

- Defect Inspection

- Profilometry

#### Litho - Scanner

- EUV High-NA 0.55

- Reduced Depth-of-Focus (focus metrology)

**KPI's**

Throughput

Accuracy

Resolution

Ease-of-Use

(simple recipes)

٠

•

Reproducibility

- Multi-litho

- > double patterning

- Combined lithography DUV + EUV

#### TECHNOLOGIES

OPTICAL METROLOGY

- Optics Design

- Sources

- Detectors

- Large Wavelength Range

- EUV/SXR Metrology

#### E-BEAM

- Metrology: single-beam

- Inspection: multi-beam

#### COMPUTATIONAL ASPECTS of OPTICAL METROLOGY

- Computational Imaging

- Aberration Correction

- Lensless Imaging

- Inverse Problems & Parameter Inference

#### SOME ACTIVITIES

(ASML)

YieldStar

•

٠

HMI – Single-beam/Multi-beam

VC Defect Inspection

Interconnect failure

**Physical Defect**

Inspection

Patterning defect

Page 16 Public

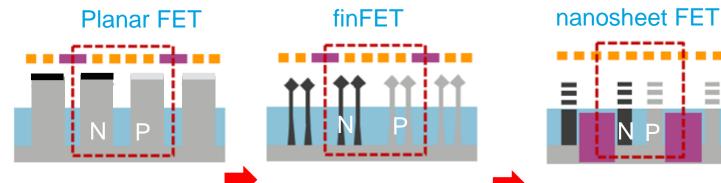

### **Metrology Needs related to Future Trends in IC-Technology**

#### Separate challenges not covered by EPE

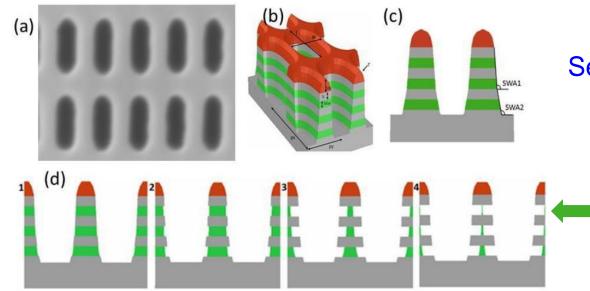

- Nanowire/Nanosheet Gate-all-around FETs with Si/SiGe/.../Si fins.

- Selective etch: Ge-recess is important KPI

- Ge-recess is not measured by EPE

Figure 4. The NWTS and the selective etch of subsurface SiGe layers is shown. A top down view of the holes in the test structure is shown in (a). A section of the optical structure model used for scatterometry simulations is shown in (b). A cross-section along the narrow part of the hole structure is shown in (c). The selective etch of the SiGe subsurface layers is shown in (d). The structures shown in (d) represent a cross-sectional view of the optimized optical model for the selectively etched structures. The amount of selective etch is (1)3.4nm, (2)10.5nm, (3)18.9nm and (4)21.9nm from the sidewall. Figure adapted from Reference 16 with copyright AIP and used with the authors' permission.

From: Alain C. Diebold, Nathaniel C. Cady, "Metrology for advanced transistor and memristor devices and materials," Proc. SPIE 11325, Metrology, Inspection, and Process Control for Microlithography XXXIV, 1132502 (2020).

### **Future Trends in IC-Technology (IMEC)**

transistor evolution according to IMEC •

3D extension via Chip-to-Chip bonding (IMEC) •

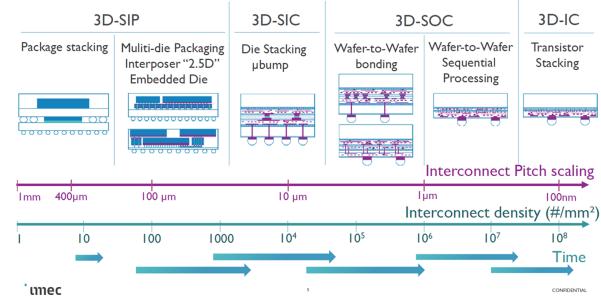

#### THE 3D INTERCONNECT TECHNOLOGY LANDSCAPE

\_

\_

$\square$